■

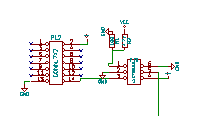

水晶発振器コンパレータ間

誤 正

上図に示したように、試作2では水晶発振器の出力を直接コンパレータ入力に繋いでいた。これは、データシートに記述されていたものをもとに設計したが、先行研究ではコンデンサと抵抗が接続されていた。

AD9851について

誤 正

上図に示したように、試作2ではAD9851のグラウンドを共通としていた。これは、グラウンドはGND、AGNDは共通で良いという指導をもとに設計をおこなったが、先行研究ではAGND,GNDを分けて設計していた。

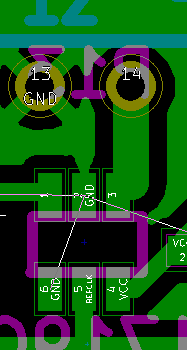

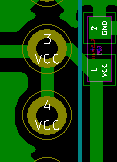

誤 正

上図に示すように試作2では電源を全て共通としていた。これは、VCCとVDDは共通でも問題ないという認識の元おこなったが、先行研究では区別していた。

誤 正

上図に示すように試作2では4-6ピン間をVCCとしていた。先行研究では抵抗により降圧しているように見えるがデータシートにはそのような記述は見当たらなかったため意図は不明である。

■

試作2のはんだ付けをおこなった。

信号線と電源間のジャンパー線用ヘッダとコンパレータに供給する電圧の分圧用に抵抗をはんだ付けした。

コンパレータは今回は表面実装にしたが次回からは変換基板を使用し使いまわしができるように配慮する。

はんだ付けした基板の写真を下に掲載する。

■

KiCAD基板データの改善と最終調整、及び確認を行った。

その後、ガーバーデータ出力を行った。

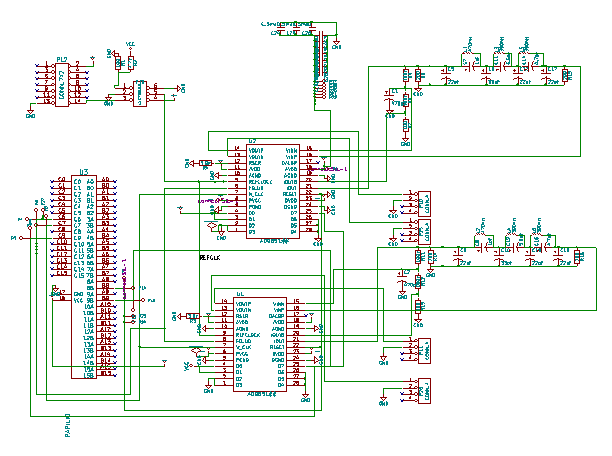

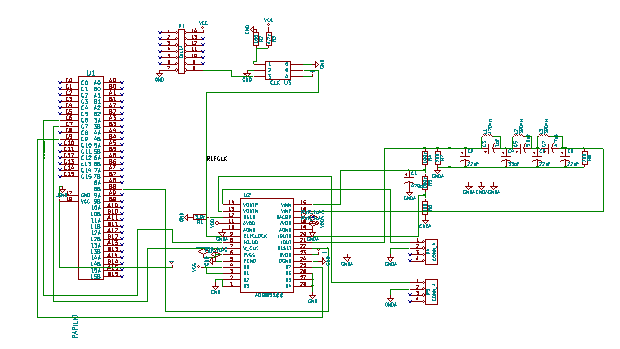

回路図

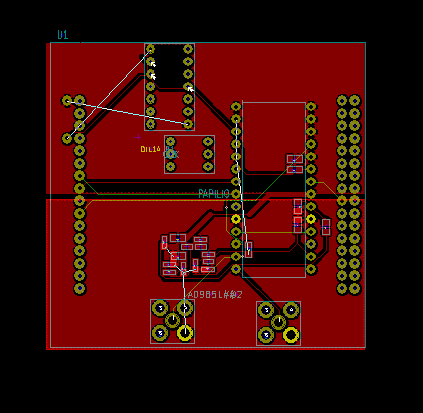

pcbnew

ガーバー

■

RESETピンの設計ミスを修正する。

前回の設計ではRESET信号を入力するべきピンがグラウンドに接続されてしまっていた。そのため動作テストではカッターによる絶縁により動作させていたが、不安があるため基盤を修正しプリントしなおすことにした。下図が問題の箇所である。

両方のAD9851においてこのような接続になっていたため修正した。また、papilio側にもRESET出力用のピンを指定していなかったのでB8に指定し新規追加作製した。

配線は配置上困難であったためジャンパ線での接続を用いた。ピンコネクタを配置するスペースが不足していたため電源配線を削除しジャンパ線での接続に切り替えることでスペースを確保した。

そのほかに前回プリントしたもので、ピン同士の位置間隔やフットプリントの大きさなどが不便であったのでところどころ微調整を行った。

出力が得られなかった原因調査の一環として入力ー出力の対応などを再確認したが問題は見られなかった。